The Nifty Chips Laboratory @ HYU

The Nifty Chips Laboratory at Hanyang University is working on cool circuits and their automatic generators.

Nifty Chips

A 18-Gb/s Variation-Tolerant Transmitter

Process: 28nm CMOS

Tapeout Year: 2022

A 28-Gb/s Single-Ended PAM-4 Receiver

Process: 40nm CMOS

Tapeout Year: 2022

A 35-Gb/s PAM-4 Transmitter

Process: 28nm CMOS

Tapeout Year: 2022

A 100-Gb/s PAM-8 Transmitter

Process: 40nm CMOS

Tapeout Year: 2021

An Asynchronous Sampling Duty-Cycle Corrector

Process: 40nm CMOS

Tapeout Year: 2021

A Transition-Limited Pulse-Amplitude Modulation Transmitter Prototype

Process: FPGA+DAC board

Year of Implementation: 2022

A 8-channel SDCSL Transceiver Array for Short-Reach Interconnects

Process: 28nm CMOS

Tapeout Year: 2021

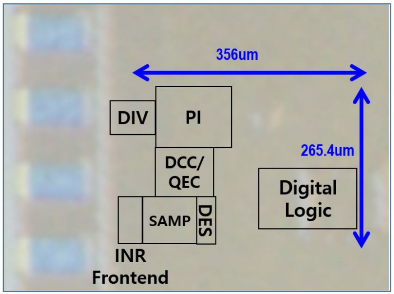

A 12Gb/s Baud-rate CDR with Integration-Hold-Reset Frontend

Process: 28nm CMOS

Tapeout Year: 2021

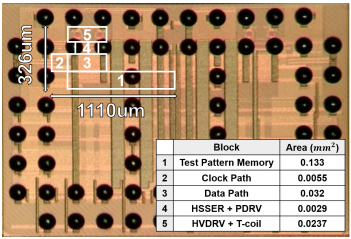

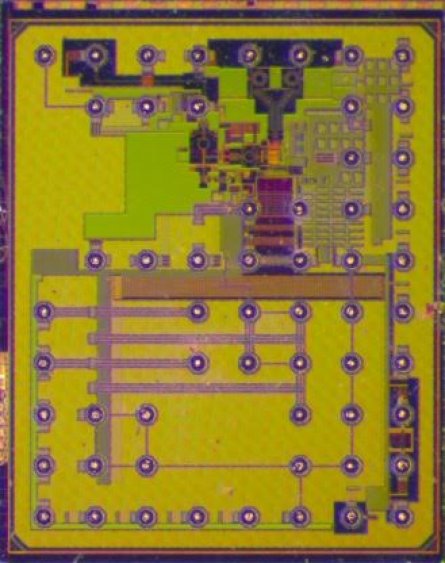

Protective PRAM Sensors Prototype

Process: 180nm CMOS

Tapeout Year: 2021

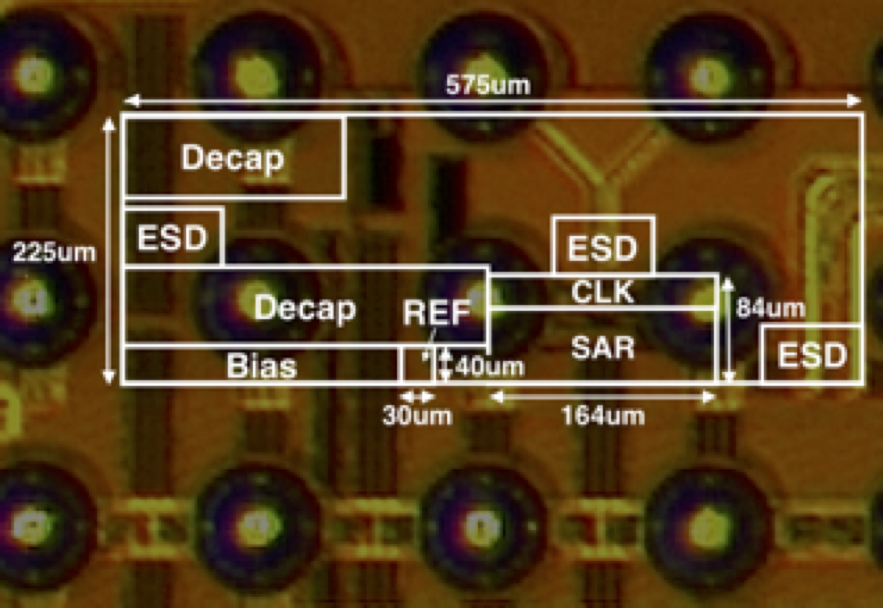

A Loop-Unrolled 1.5GS/s SAR ADC

Process: 28nm CMOS

Tapeout Year: 2021

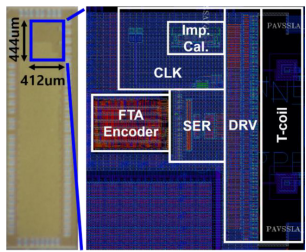

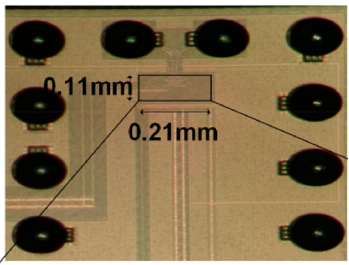

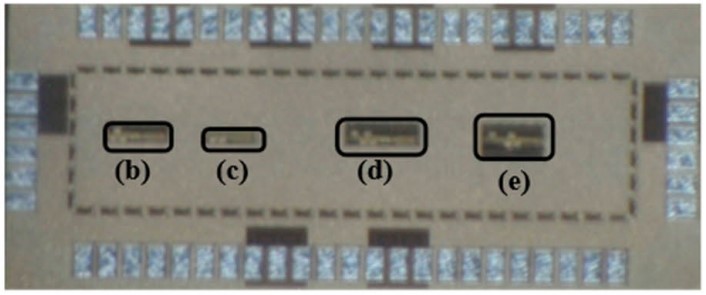

A PAM4 Driver Prototype

Process: 40nm CMOS

Tapeout Year: 2020

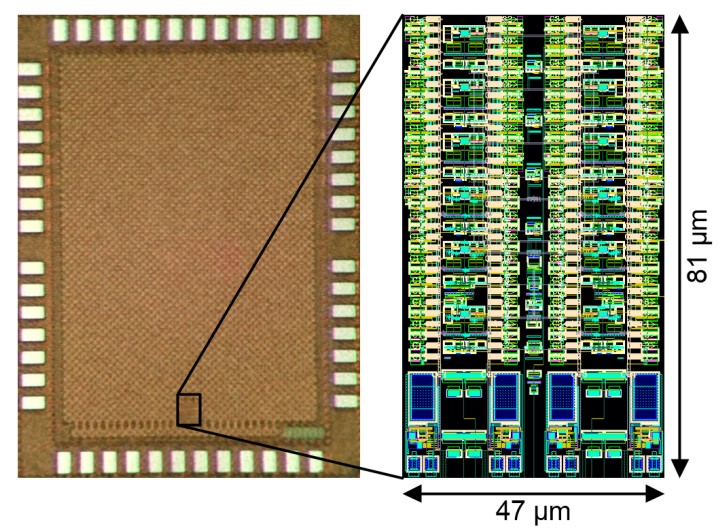

A 4-wire Balanced-Single-Ended Signaling Transceiver Array

Process: 28nm CMOS

Tapeout Year: 2019

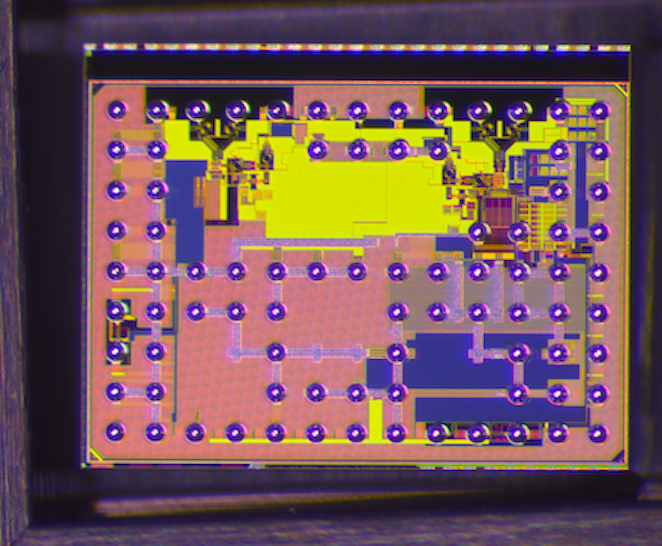

A Generated 7GS/s 8b Time-Interleaved SAR ADC Integrated to a Signal Analysis SoC

Process: 16nm CMOS FinFET

Tapeout Year: 2016

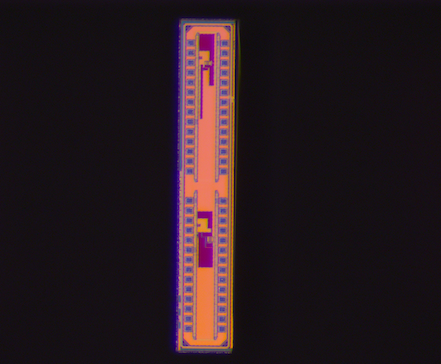

A Generated SAR ADC Prototype

Process: 28nm CMOS

Tapeout Year: 2015

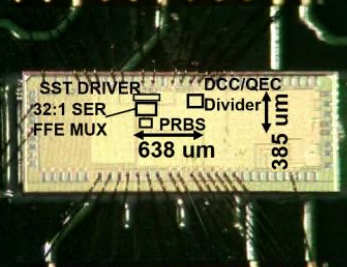

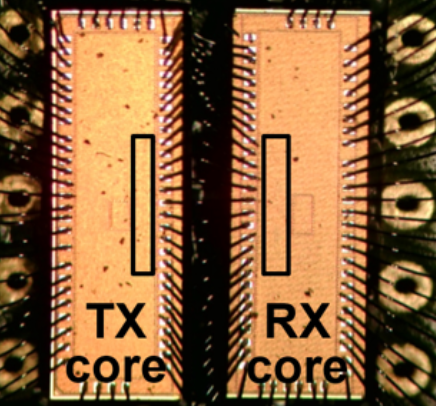

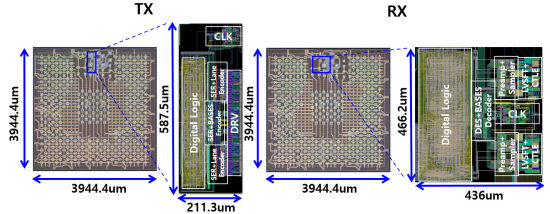

A Complete 60Gb/s Transceiver

Process: 65nm CMOS

Tapeout Year: 2015

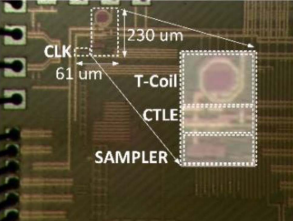

A 60Gb/s Receiver Frontend

Process: 65nm CMOS

Tapeout Year: 2014

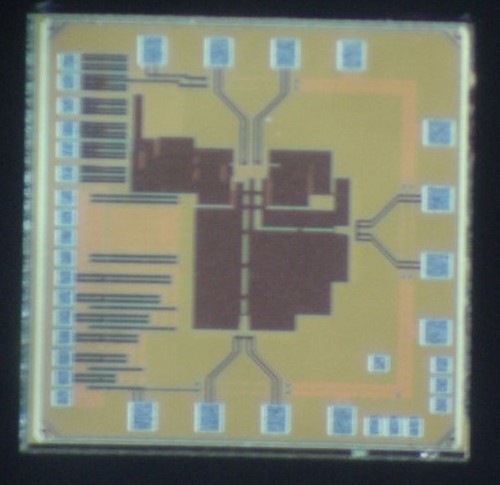

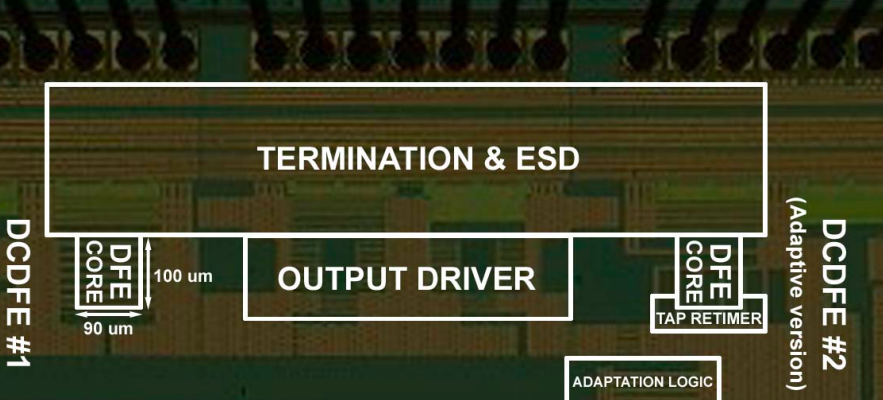

A 5Gb/s Digitally-Controlled Decision Feedback Equalizer

Process: 130nm CMOS

Tapeout Year: 2008